The Islamic University – Gaza Deanery of Graduate Studies Faculty of Engineering Electrical Engineering

الجامعة الإسلامية – غزة عمادة الدراسات العليا كلية الهندســــة الهندسة الكهريانية

## Sun and Maximum Power Point Tracking in Solar Array Systems Using Fuzzy Controllers Via FPGA

Mohammed S. EL-Moghany

Advisor **Dr. Basil Hamed**

This Thesis is submitted in Partial Fulfillment of the Requirements for the Degree of Master of Science in *Electrical Engineering*

1432ه - 2011 م

## **Dedication**

# To my parents, big brother, sisters, wife, and lovely kids

Mohammed Saker Elmoghany

### **Acknowledgments**

At the beginning, I thank ALLAH for giving me the strength and health to let this work see the light.

I wish to express my deepest gratitude to my advisor, Dr. Basil Hamed, for his professional assistance, support, advice and guidance throughout my thesis, and to my discussion committee, Dr. Hatem El Aydi and Dr. Assad Abu Jasser for their acceptance to discuss my thesis.

I would also like to extend my gratitude to my family for providing all the preconditions necessary to complete my studies.

### <u>Abstract</u>

### Sun and Maximum Power Point Tracking in Solar Array Systems Using Fuzzy Controllers Via FPGA

By Mohammed S. EL-Moghany

Solar energy is viewed as clean and renewable source of energy for the future. So the use of Photovoltaic systems has increased in many applications. That need to improve the materials and methods used to harness this power source. There are two major approaches; sun tracking and maximum power point tracking. These two methods need efficient controllers. The controller may be conventional or intelligent such as Fuzzy Logic Controller (FLC). FLCs have the advantage to be relatively simple to design as they do not require the knowledge of the exact model and work well for nonlinear system. To implement this controller, Field Programmable Gate Array (FPGA) can be used. This method has many advantages over classical microprocessors.

In this research, Two fuzzy logic controllers are fabricated on modern FPGA card (Spartan-3AN, Xilinx Company, 2009) to increase the energy generation efficiency of solar cells. These controllers are, sun tracking controller and maximum power point tracking controller.

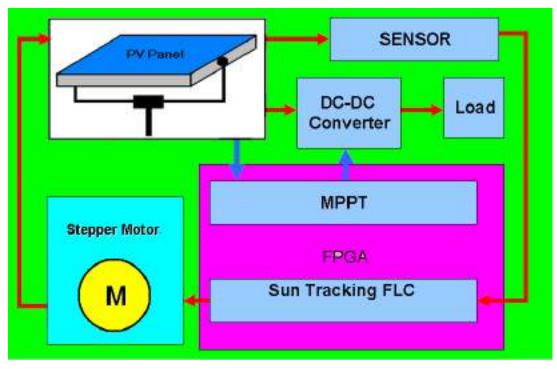

Sun tracking generating power system is designed and implemented in real time. A tracking mechanism composed of photovoltaic module, stepper motor, sensors, input/output interface and expert FLC controller implemented on FPGA, that to track the sun and keep the solar cells

always face the sun in most of the day time. The proposed sun tracking controller is tested using Matlab/Simulink program, the results show that the controller have a good response.

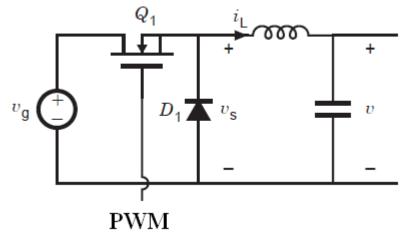

Maximum power point tracking system is designed and implemented. The system composed of photovoltaic module, buck converter and the fuzzy logic controller implemented on FPGA for controlling on/off time of MOSFET switch of a buck converter. The proposed maximum power point tracking controller for grid-connected photovoltaic system is tested using model designed by Matlab/Simulink program with graphical user interface (GUI) for entering the parameters of any array model using information from its datasheet, the results show that the controller have a response better than conventional controller applied on the same system.

#### ملخص البحث

### تتبع الشمس وتتبع أقصى قيمة للقدرة في مصفوفات الخلايا الشمسية باستخدام متحكمات ضبابية بتقنية ال FPGA

#### إعداد محمد صقر المغنى

تعتبر الطاقة الشمسية احد مصادر الطاقة النظيفة والمتجددة، والأقل تلويثاً للبيئة وهي مصدر لا ينضب أكثر من كل مصادر الطاقة الأخرى المعروفة. وهذا أدى إلى ازدياد عدد التطبيقات التي تستخدم ألواح الخلايا الشمسية. وهذا يتطلب تحسين المواد والطرق المستعملة لتسخير مصدر الطاقة هذا. هناك طريقتان رئيسيتان لزيادة القدرة المتحصل عليها من الأنظمة الشمسية وهي تتبع مكان الشمس وتتبع النقطة التي تكون عندها القدرة أقصى ما يمكن. وكلا الطريقتين يحتاج إلى متحكم. هذا المتحكم إما يكون من نوع تقليدي أو من نوع ذكي مثل المتحكمات الضبابية. حيث أن المتحكم الضبابي مميزات مثل سهولة نسبية في التصميم فهو لا يحتاج معرفة دقيقة عن المعادلات الرياضية التي تصف النظام المراد التحكم به، وهو يعمل بشكل أفضل مع الأنظمة اللاخطية. ولكي نبني هذا المتحكم فإنه يفضل استخدام تقنية مصفوفة البوابات القابلة للبرمجة الحقلية (FPGA). وهذه الطريقة لها عدة مميزات عن المعالجات الدقيقة .

في هذا البحث تم اقتراح فكرة مطورة في هذا المجال وهي بناء متحكمين ضبابيين على بطاقة (FPGA) حديثة من طراز (Spartan-3AN) من إنتاج شركة زيلنكس عام 2009 م . أحد المتحكمين لجعل لوح الخلايا الشمسية يتتبع الشمس، والمتحكم الأخر ليتتبع النقطة التي تكون عندها القدرة أقصى ما يمكن. وذلك لزيادة كفاءة الخلايا الشمسية في توليد الطاقة.

تم تصميم وتطبيق متتبع الشمس والذي يتكون من : لوح من الخلايا الشمسية، مجسات، موتور الخطوة، موصلات للمداخل والمخارج، و متحكم ضبابي تم عمله على بطاقة (FPGA) وذلك لإبقاء لوح الخلايا الشمسية تواجه الشمس أغلب النهار. وتم اختبار المتحكم باستخدام برنامج السيميولينك التابع لبرنامج الماتلاب وكانت النتيجة أن استجابة المتحكم بشكل حسن.

تم تصميم وتطبيق نظام تتبع أقصى نقطة للقدرة، والمكون من لوح خلايا شمسية، محول من نوع (Buck) و متحكم ضبابي تم عمله على بطاقة (FPGA) وذلك للتحكم في فتح و إغلاق مفتاح ال (MOSFET) الموجود داخل المحول. وتم اختبار المتحكم باستخدام برنامج السيميولينك ، عن طريق مودل تم تصميمه ليحاكي سلوك أي مصفوفة خلايا شمسية ذو واجهة مرسومة للمستخدمين باستخدام برنامج (GUI) التابع لبرنامج الماتلاب وذلك لإدخال قيم المتغيرات للمصفوفة و التي يضعها المنتِج في دليل مواصفات المنتَج، لإختبار سلوك هذه المصفوفة وتأثير المتحكم عليه. وكانت نتيجة فحص المتحكم الضبابي أفضل من النتيجة المتحصل عليها من متحكم أخر تقليدي تم تطبيقه على نفس النظام.

## Table of Contents

| СНАРТ       | <u>`ER 1</u> Introduction               | 1  |

|-------------|-----------------------------------------|----|

| 1.1         | Introduction                            | 2  |

| 1.2         | Motivation                              | 4  |

| 1.3         | Objectives                              | 4  |

| 1.4         | Literature Review                       | 4  |

| 1.5         | Contribution                            | 6  |

| 1.6         | Outline Of The Thesis                   | 6  |

| Introdu     | ction to Solar Energy                   | 7  |

| 2.1         | Background                              | 8  |

| 2.1.1       | Renewable Energy                        | 8  |

| 2.1.2       | Solar Energy                            | 9  |

| 2.2         | Photovoltaic Background:                | 9  |

| 2.3         | Principle of Solar Cells                | 10 |

| 2.4         | Types of Solar Panels                   |    |

| 2.5         | Equivalent Circuit of a Solar Cell      | 12 |

| 2.6         | Balance Of System (BOS):                | 14 |

| 2.7         | Sun Tracker                             | 15 |

| 2.8         | Maximum Power Point Tracking            | 15 |

| 2.9         | Pulse Width Modulation (PWM)            | 18 |

| 2.10        | Buck Converter                          | 19 |

| <u>CHAP</u> | <u>`ER 3</u>                            | 20 |

| Fuzzy L     | ogic Control                            | 20 |

| 3.1         | Introduction                            | 21 |

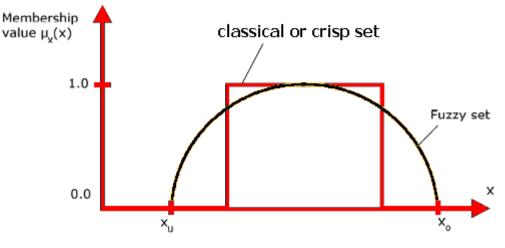

| 3.2         | Fuzzy Sets                              | 21 |

| 3.2         | .1 Basic Concepts                       | 21 |

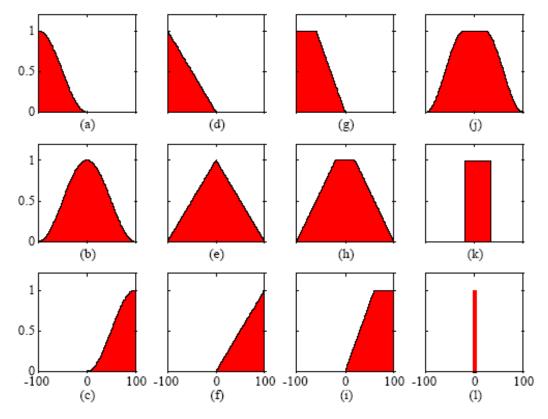

| 3.2         | .2 Basic Operations on Fuzzy Sets       | 23 |

| 3.3         | Fuzzy Logic :                           |    |

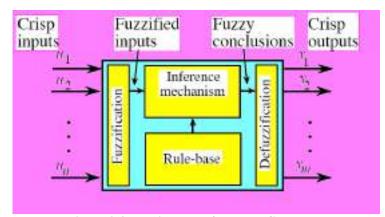

| 3.4         | Fuzzy Logic Controller Structure        | 27 |

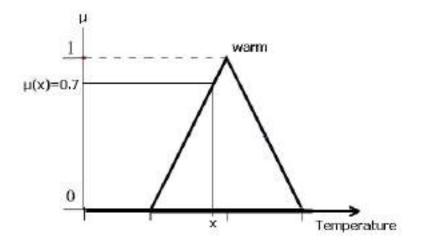

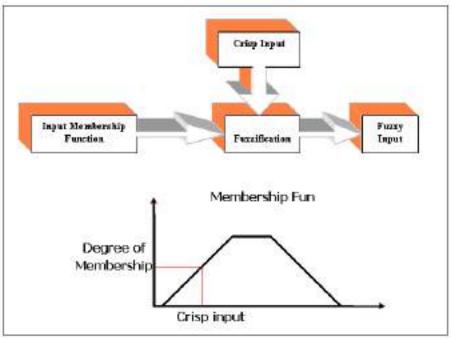

| 3.4         | .1 Fuzzification                        | 27 |

| 3.4         | .2 Knowledge Base:                      | 28 |

| 3.4         | .3 Fuzzy Inference Engine               | 30 |

| -           | 3.4.3.1 Mamdani Fuzzy Model             |    |

|             | <b>3.4.3.2</b> Sugeno Method            |    |

| 3.4         |                                         |    |

| <b>CHAP</b> |                                         |    |

|             | ogrammable Gate Arrays (FPGAs)          |    |

| 4.1         | Introduction                            |    |

| 4.2         | FPGAs Architecture                      |    |

| 4.3         | FPGA Programming Technologies:          |    |

| 4.4         | Fuzzy Controller Design using FPGA      |    |

| 4.5         | Xilinx Spartan-3AN FPGA Starter Kit:    |    |

| <u>CHAP</u> |                                         |    |

| Designi     | ng Sun Tracker System Using FLC on FPGA | 54 |

| 5.1     | Overall System Design and Implementation                   | 55  |

|---------|------------------------------------------------------------|-----|

| 5.2     | Sun Tracker                                                | 55  |

| 5.3     | Sensors:                                                   | 56  |

| 5.3.1   | Photo Sensor:                                              |     |

| 5.3.2   | Tracking Sensor Design                                     | 56  |

| 5.3.3   | LDR Connection:                                            |     |

| 5.3.4   | Position Sensor:                                           |     |

| 5.3.5   | Analog to Digital Converter (ADC)                          | 60  |

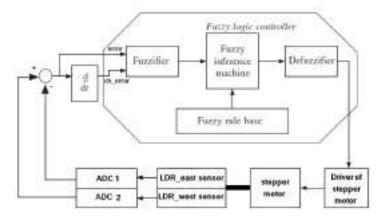

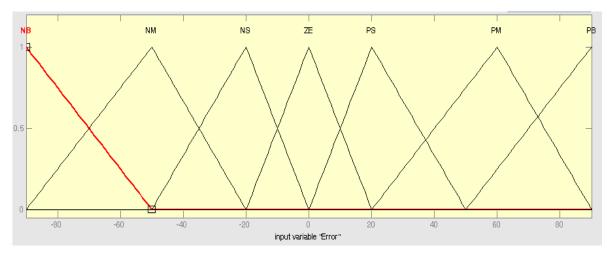

| 5.4     | Fuzzy Logic Controller:                                    | 61  |

| 5.4.1   | FLC design                                                 |     |

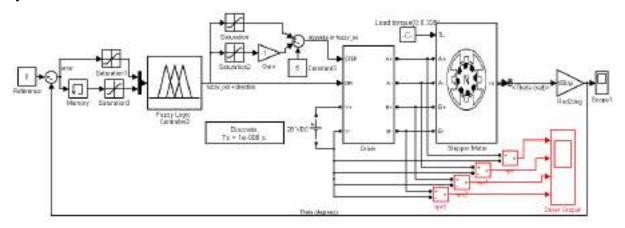

| 5.4.2   | Fuzzy Logic Controller Simulation on Matlab/Simulink:      | 64  |

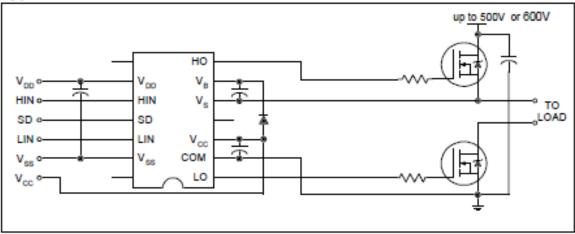

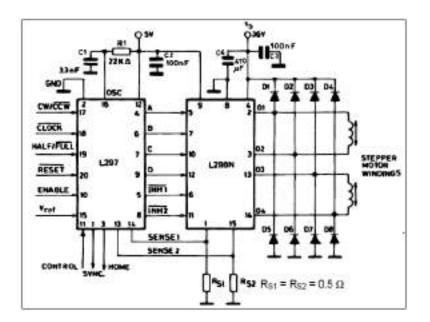

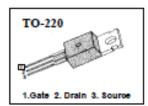

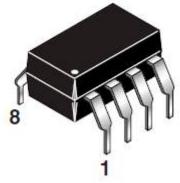

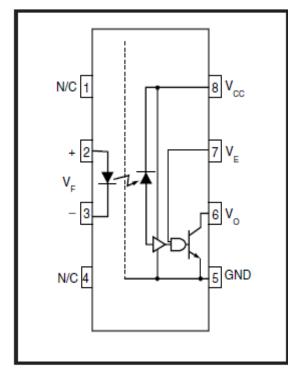

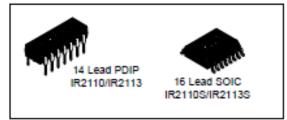

| 5.5     | Stepper Motor Driver:                                      | 66  |

| 5.6     | Implementing Fuzzy Logic Controller on an FPGA:            | 69  |

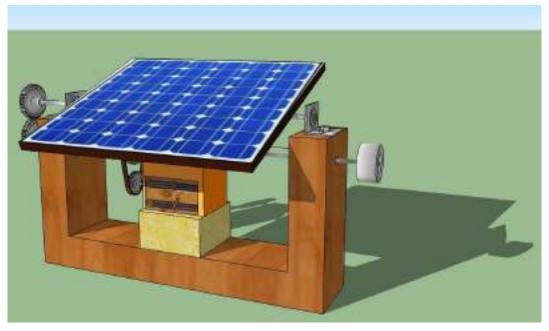

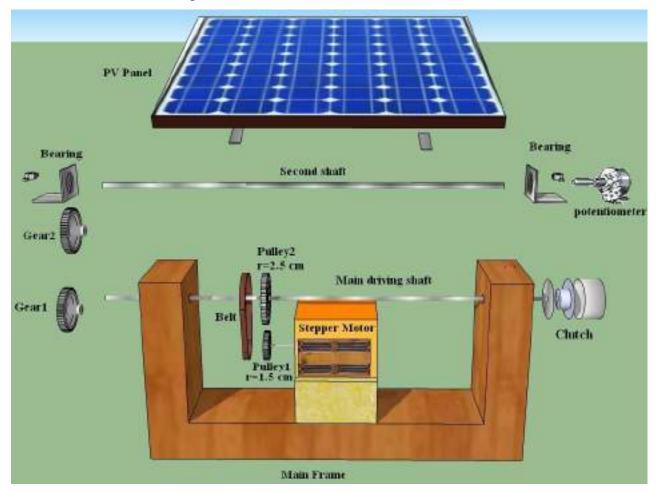

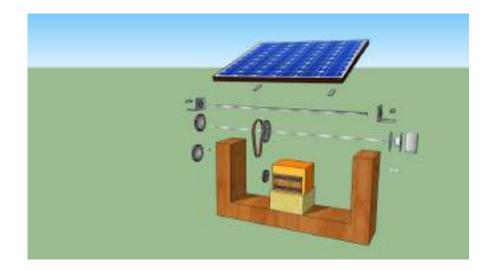

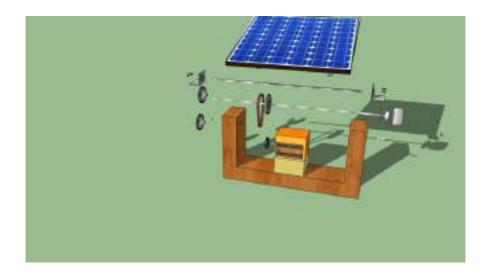

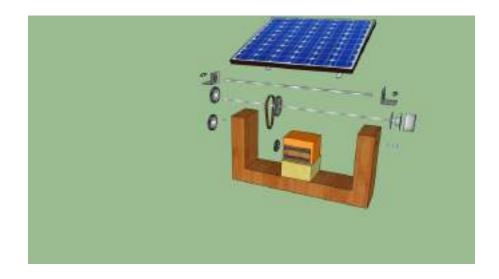

| 5.7     | Mechanical Construction and Components:                    | 72  |

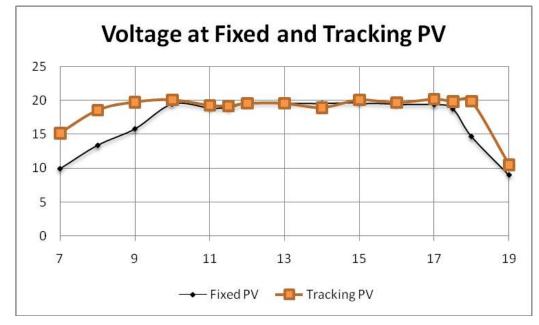

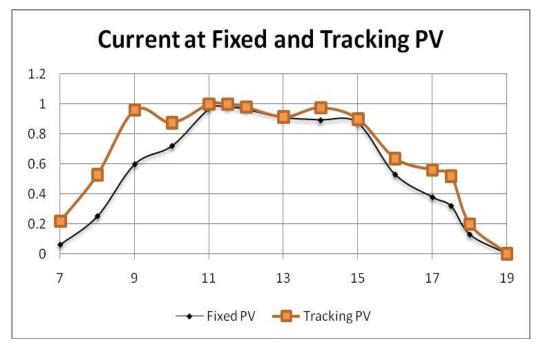

| 5.8     | Experimental Results:                                      | 74  |

|         | <u>`ER 6</u>                                               |     |

| Designi | ng MPPT System Using FLC on FPGA                           | 77  |

| 6.1     | MPPT of PV Using Fuzzy Controller:                         |     |

| 6.2     | MPPT Fuzzy Logic Controller:                               | 78  |

| 6.3     | MPPT Fuzzy Logic Controller Simulation on Matlab/Simulink: | 82  |

| 6.3     | .1 PV modeling for Simulation                              | 82  |

| 6.3     | .2 GUI Interface for PV Model:                             | 83  |

| 6.3     | .3 Control Signal Generation in Simulation                 | 84  |

| 6.3     | v 8                                                        |     |

| 6.4     | Comparison Between FLC and Conventional Controller:        |     |

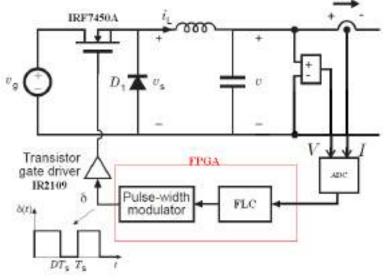

| 6.5     | Implementing the Maximum Power Point Tracker:              | 87  |

| 6.5     | 1 0                                                        |     |

| 6.5     | 1 8                                                        |     |

|         | .3 Experimental Results:                                   |     |

| СНАРТ   | <u>`ER 7</u> Conclusion and Scope for Future Work          |     |

| 7.1     | Conclusion                                                 |     |

| 7.2     | Scope for Future Work                                      |     |

|         | <u>ces:</u>                                                |     |

|         | <u>ices</u>                                                |     |

| 1.1     | Appendix A                                                 |     |

| 1.2     | Appendix B:                                                |     |

| 1.3     | Appendix C:                                                |     |

| 1.4     | Appendix D:                                                |     |

| 1.5     | Appendix E:                                                |     |

| 1.6     | Appendix F:                                                |     |

| 1.7     | Appendix G:                                                | 112 |

## List of Tables

| Table 5-1: Control rule base for fuzzy controller                            | 63 |

|------------------------------------------------------------------------------|----|

| Table 5-2: Full-step phase sequence                                          | 66 |

| Table 5-3: Experimental results of fixed angle type and tracking system      | 74 |

| Table 6-1: Control rule base for MPPT fuzzy controller.                      | 81 |

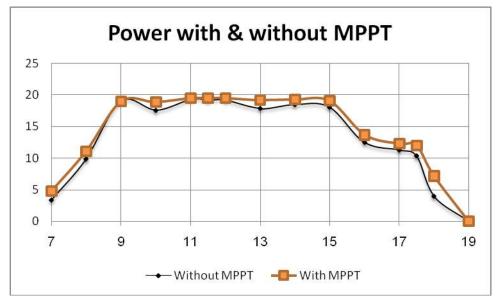

| Table 06-2: Comparison of the experimental results obtained with and without |    |

| using MPPT & sun tracker (ST) controller                                     | 92 |

## List of Figures :

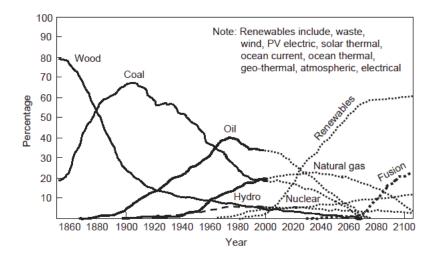

| Figure 2-1: Future global energy consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2-2: Principle of solar cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10 |

| Figure 2-3:         Monocrystalline         Solar         Panels         Panels | 11 |

| Figure 2-4: Polycrystalline Solar Panels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 11 |

| Figure 2-5: Amorphous Solar Panels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12 |

| Figure 2-6: Equivalent Circuit of Solar Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13 |

| Figure 2-7: Characteristic I-V curve of a practical photovoltaic device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13 |

| Figure 2-8: Current-voltage characteristic of a PV module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16 |

| Figure 2-9: Power-voltage characteristic of a PV module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16 |

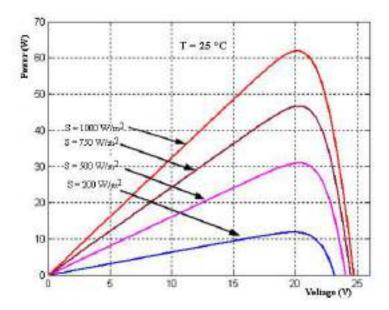

| Figure 2-10: Influence of the solar radiation for constant temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 17 |

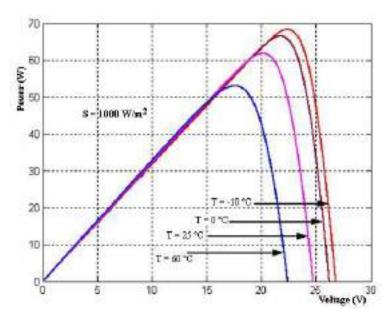

| Figure 2-11: Influence of the temperature of junction for constant irradiation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17 |

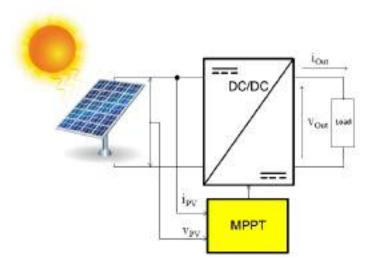

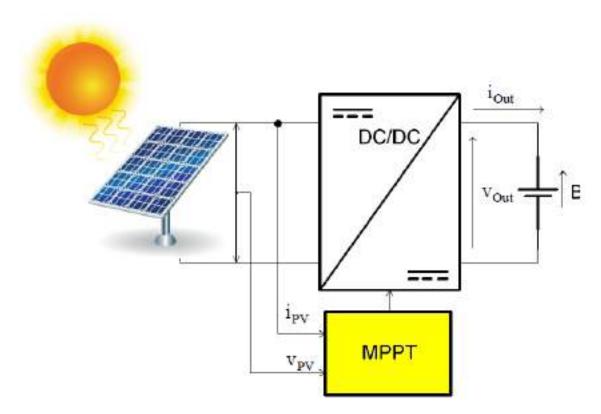

| Figure 2-12: Photovoltaic with MPPT system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 18 |

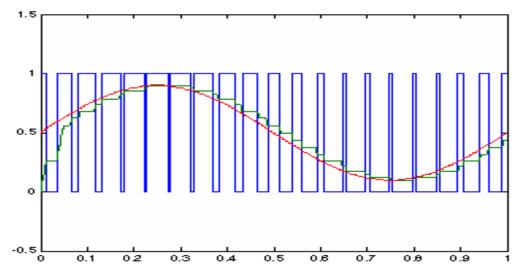

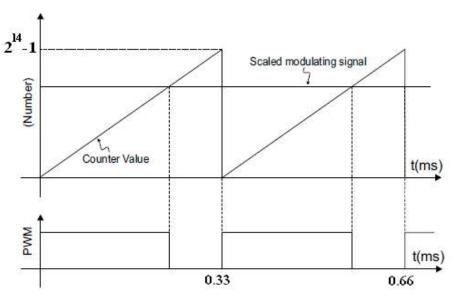

| Figure 2-13: Pulse width modulation waveforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18 |

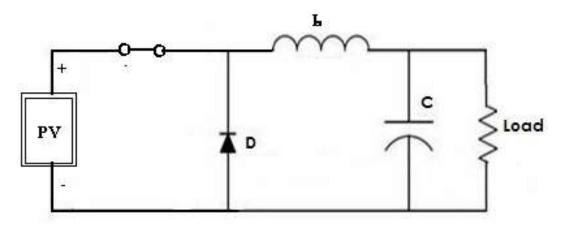

| Figure 2-14: Buck converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19 |

| Figure 3-1: Fuzzy and Classical sets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22 |

| Figure 3-2: Different shapes of membership functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23 |

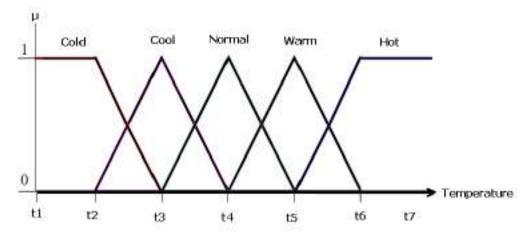

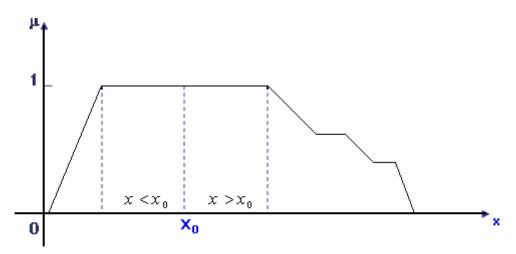

| Figure 3-3: membership function example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 24 |

| Figure 3-4: Universe of discourse for linguistic variable: temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24 |

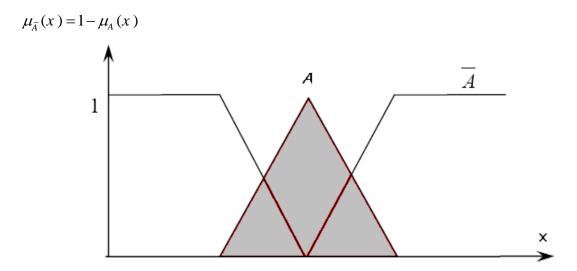

| Figure 3-5: Complement of fuzzy sets A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25 |

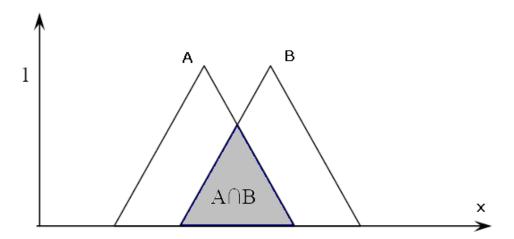

| Figure 3-6: Intersection of fuzzy sets A and B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25 |

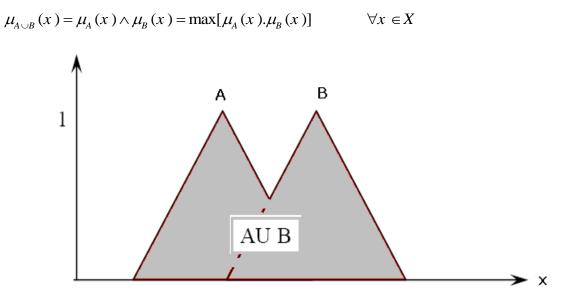

| Figure 3-7: Union of fuzzy sets A and B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26 |

| Figure 3-8: Basic parts of a Fuzzy Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27 |

| Figure 3-9: Fuzzification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 28 |

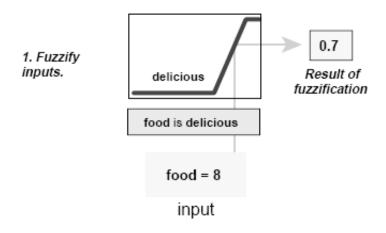

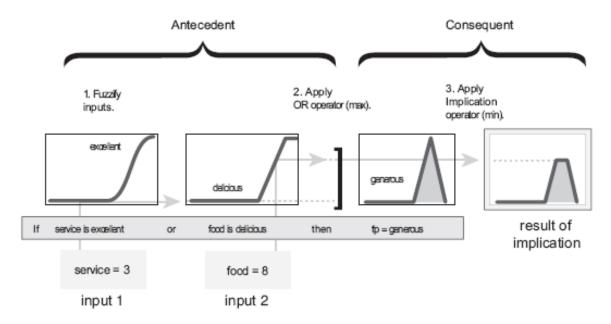

| Figure 3-10: Fuzzify input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 32 |

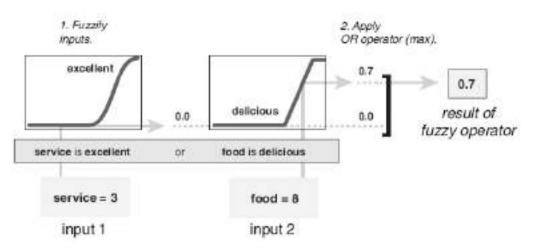

| Figure 3-11: Appling OR operator to multiple part antecedents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33 |

| Figure 3-12: Appling implication method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 33 |

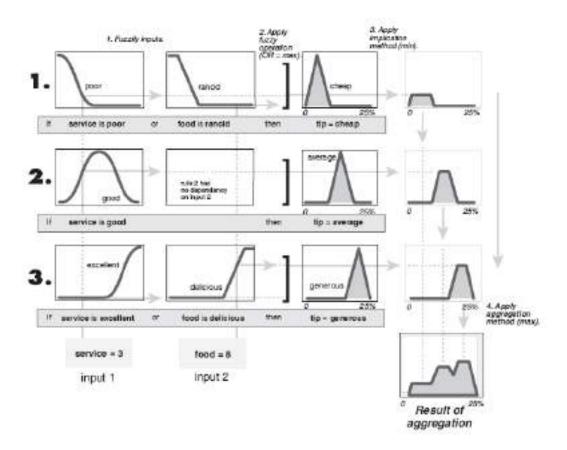

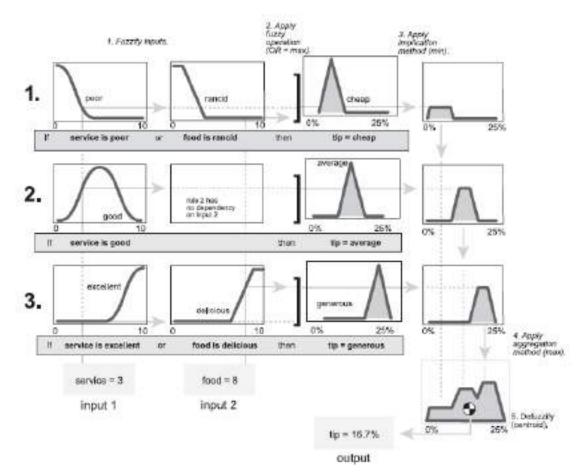

| Figure 3-13: Aggregating all Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 34 |

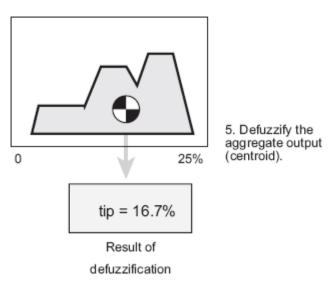

| Figure 3-14: Defuzzification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 35 |

| Figure 3-15: Full-size fuzzy inference diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

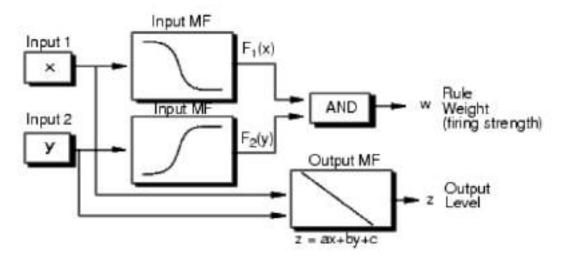

| Figure 3-16: Sugeno rule Operation                                    | 37 |

|-----------------------------------------------------------------------|----|

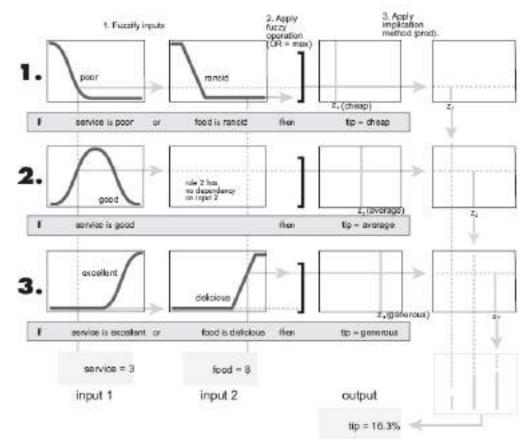

| Figure 3-17: Fuzzy tipping model                                      | 38 |

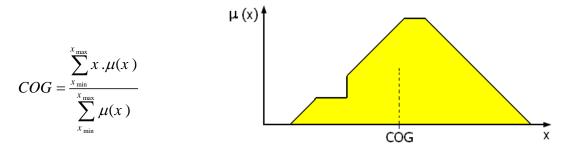

| Figure 3-18: Center of gravity (COG) defuzzification method           | 40 |

| Figure 3-19: Middle of maxima (MOM) defuzzification method            | 41 |

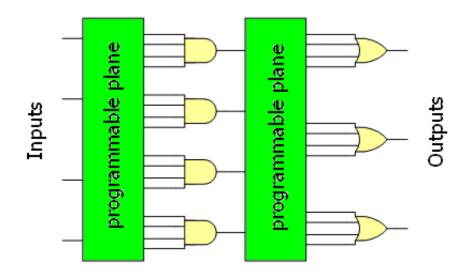

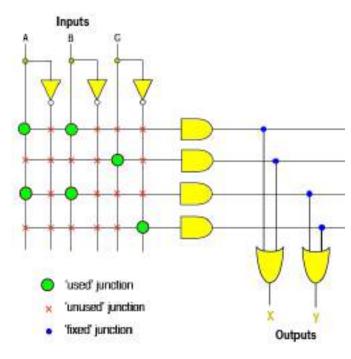

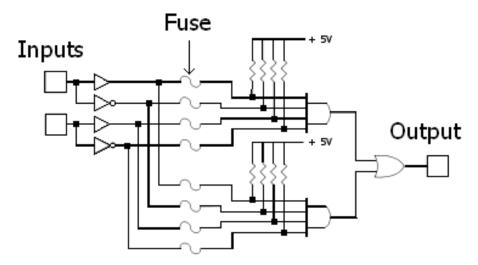

| Figure 4-1: PLA constructions                                         | 44 |

| Figure 4-2: PAL architecture                                          | 45 |

| Figure 4-3: Simplified programmable logic device                      | 45 |

| Figure 4-4: CPLD architecture                                         | 46 |

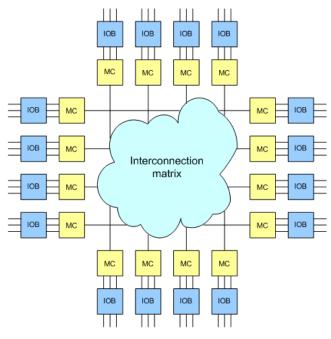

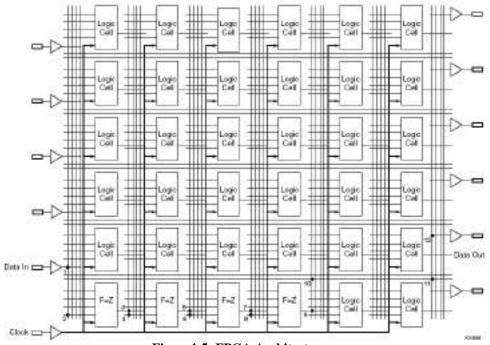

| Figure 4-5: FPGA Architecture                                         | 47 |

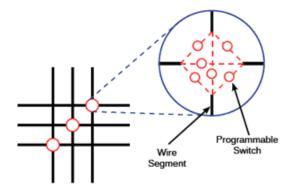

| Figure 4-6: Routing Switch Box                                        | 48 |

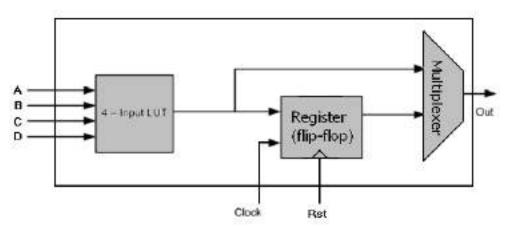

| Figure 4-7: FPGA logic element.                                       | 48 |

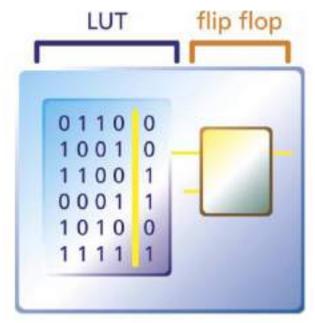

| Figure 4-8: SRAM Logic Cell.                                          | 49 |

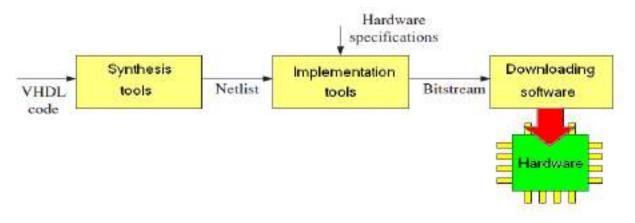

| Figure 4-9: Simplified block diagram of the hardware design process   | 51 |

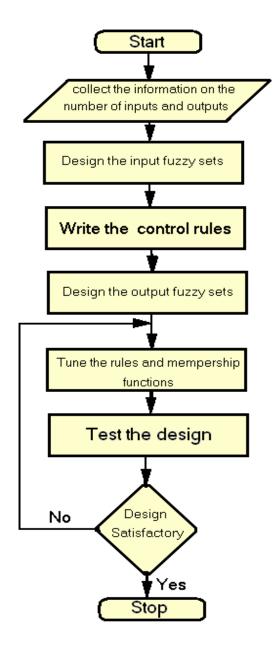

| Figure 4-10: Design steps for an FLC using an FPGA                    | 52 |

| Figure 4-11: Spartan-3AN Starter Kit Board                            | 53 |

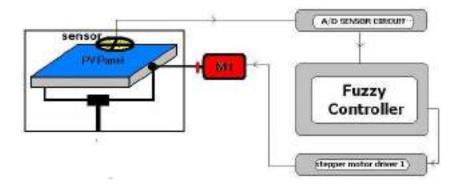

| Figure 5-1: Block diagram for the Overall control system              | 55 |

| Figure 5-2: Block diagram for the sun tracker system                  | 56 |

| Figure 5-3: Different LDR sensors                                     | 56 |

| Figure 5-4: How sensor work                                           | 57 |

| Figure 5-5: Tracking Sensor Internal Design                           | 57 |

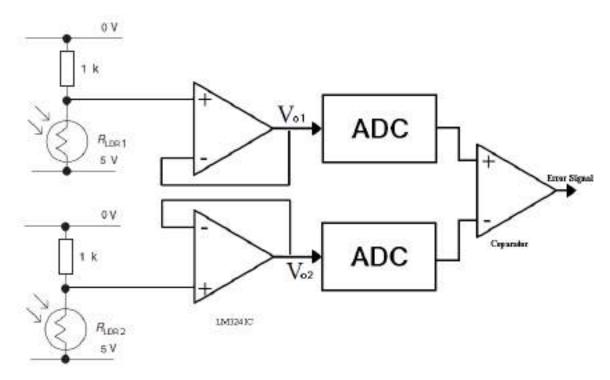

| Figure 5-6: LDR connection                                            | 58 |

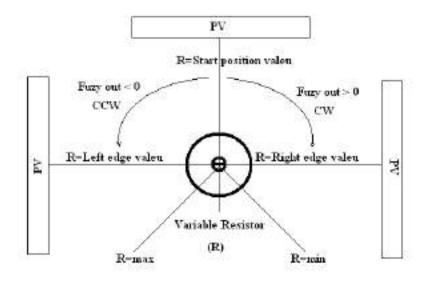

| Figure 5-7: Position sensor                                           | 59 |

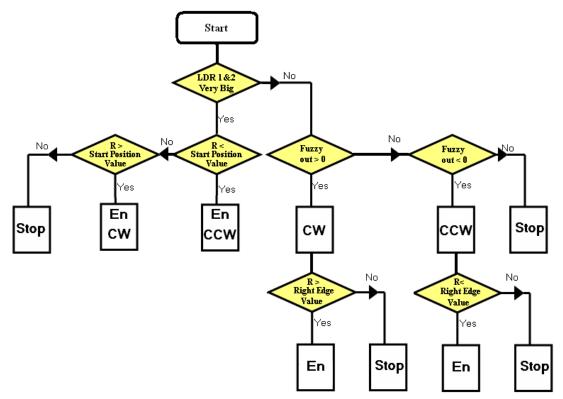

| Figure 5-8: Motor Control Signals algorithm                           | 59 |

| Figure 5-9: The ideal ADC input/output characteristic                 | 60 |

| Figure 5-10: FLC controller for the sun tracker system                | 61 |

| Figure 5-11: Error and change in error approach in FLC                | 61 |

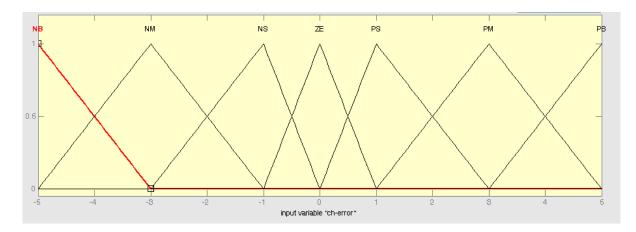

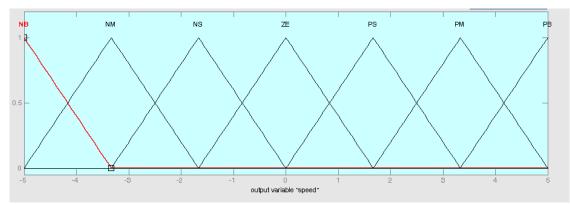

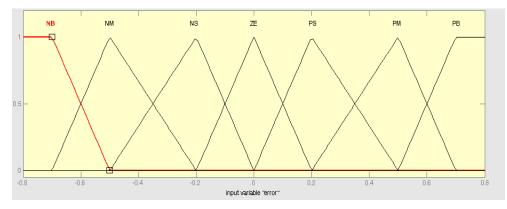

| Figure 5-12: Error fuzzy set of FLC                                   | 62 |

| Figure 5-13: Change in error fuzzy set of FLC                         | 62 |

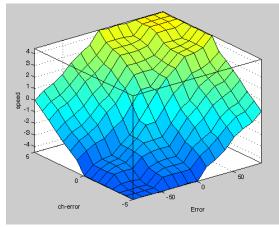

| Figure 5-14: Fuzzy set of FLC output entering to stepper motor driver | 63 |

| Figure 5-15: Rule surface of FLC                                      | 64 |

| Figure 5-16: Fuzzy logic controller                                   | 64 |

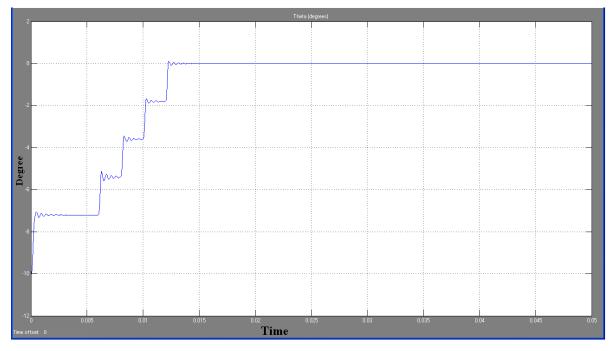

| Figure 5-17: Output Degree                                                               | 65 |

|------------------------------------------------------------------------------------------|----|

| Figure 5-18: A zoom for one motor step                                                   | 65 |

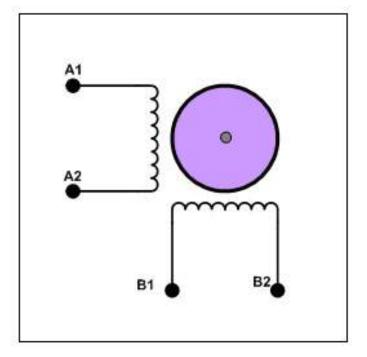

| Figure 5-19: Bipolar Stepper Motor                                                       | 66 |

| Figure 5-20: The output of the driver                                                    | 67 |

| Figure 5-21: Stepper motor driver as block diagram                                       | 67 |

| Figure 5-22: Stepper motor driver PCB kit                                                | 68 |

| Figure 5-23: FLC on FPGA card                                                            | 69 |

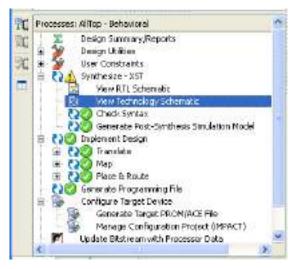

| Figure 5-24:         VHDL language in Xilinx_ISE 11.1 software program                   | 69 |

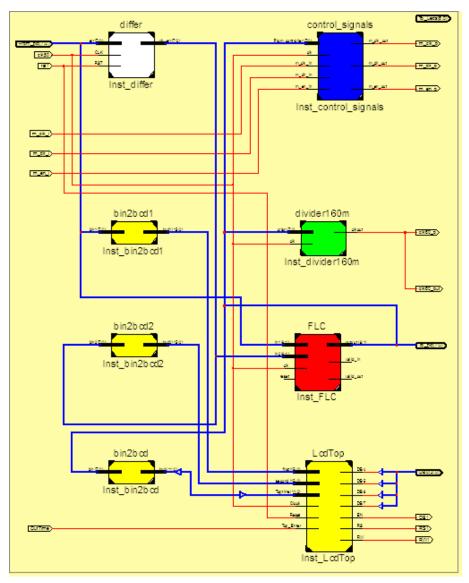

| Figure 5-25: RTL schematic diagram for the FLC with other blocks                         | 70 |

| Figure 5-26: Converting a VHDL design to a hardware design processes                     | 71 |

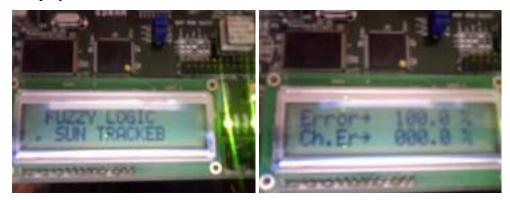

| Figure 5-27: FLC I/O on LCD of the FPGA card                                             | 71 |

| Figure 5-28: Complete sun tracker system                                                 | 72 |

| Figure 5-29: System prototype                                                            | 72 |

| Figure 5-30: Mechanical construction and components                                      | 73 |

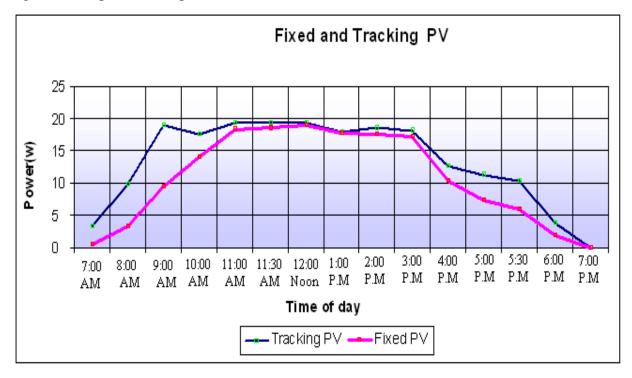

| Figure 5-31: The voltage comparison of fixed angle PV and tracking PV system             | 75 |

| Figure 5-32: The current comparison of fixed angle PV and tracking PV system             | 75 |

| Figure 5-33: The power comparison of fixed angle type and tracking PV system             | 76 |

| Figure 6-1: Maximum Power Point Tracker (MPPT) system as a block diagram                 | 78 |

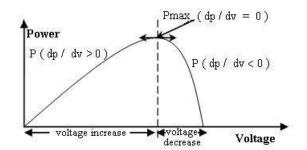

| Figure 6-2: Power-voltage characteristic of a PV module                                  | 79 |

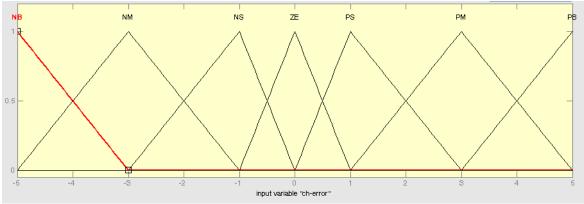

| Figure 6-3: Membership function of error (E)                                             | 79 |

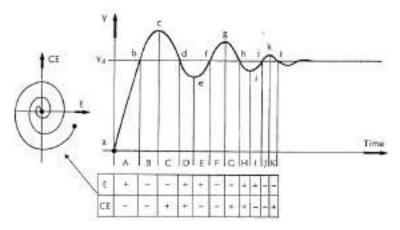

| Figure 6-4: Membership function of change of error (CE)                                  | 80 |

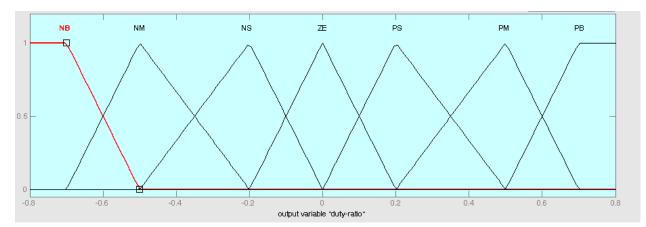

| Figure 6-5: Membership function of duty ratio (D)                                        | 80 |

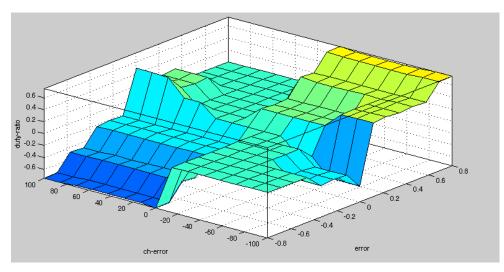

| Figure 6-6: Rule surface of FLC                                                          | 81 |

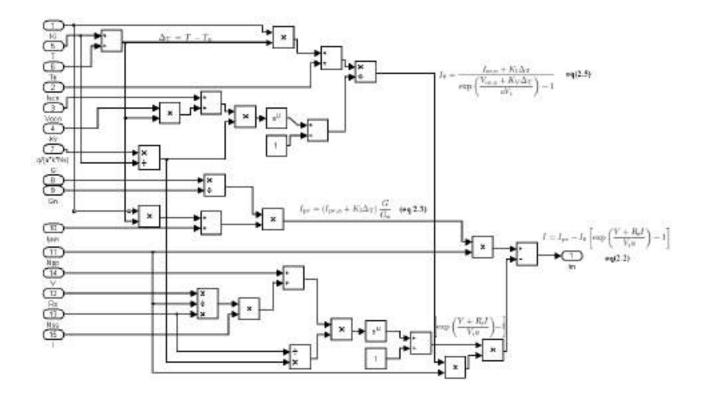

| Figure 6-7: Modeling of the current generated by PV array in matlab simulink             | 82 |

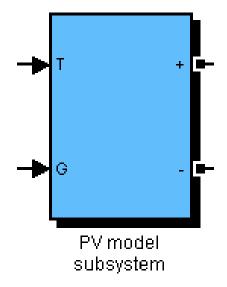

| Figure 6-8: PV model Subsystem                                                           | 83 |

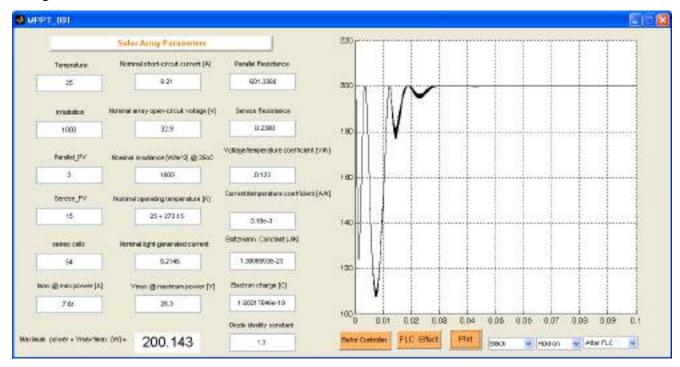

| <b>Figure 6-9:</b> GUI for entering the parameters of any array model from its datasheet | 83 |

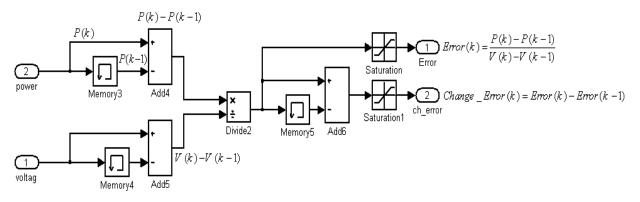

| Figure 6-10: Generating the Error and Change in Error Signals                            | 84 |

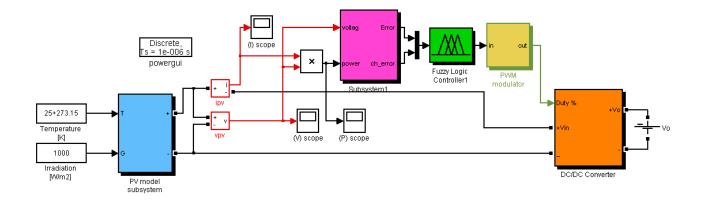

| Figure 6-11: Controlling the PV power using FLC                                          | 84 |

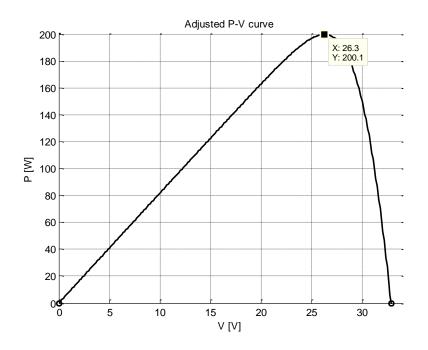

| Figure 6-12: The Characteristic P-V curve before adding the FLC                          | 85 |

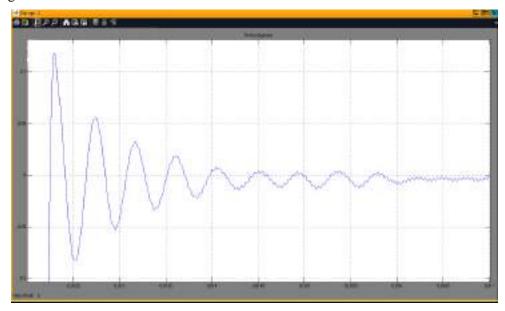

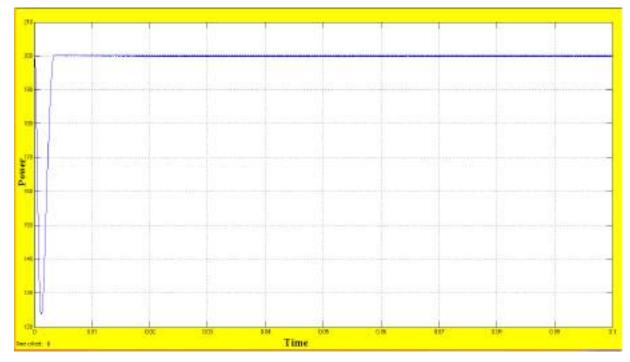

| Figure 6-13: Controller effect on the power                                              | 86 |

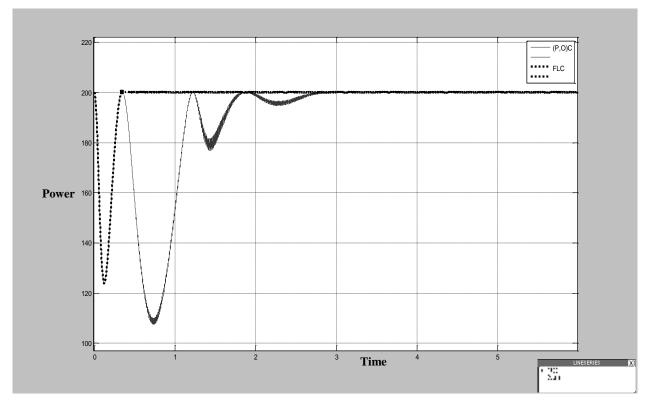

| Figure 6-14: Effect of the controllers P&O and FLC on PV power out                       | 87 |

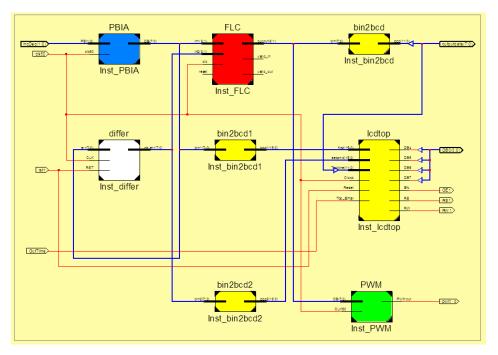

| Figure 6-15: RTL schematic diagram for the FLC with other blocks          | 88 |

|---------------------------------------------------------------------------|----|

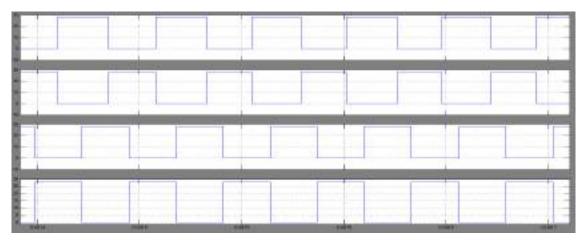

| Figure 6-16: Generating PWM signals                                       | 88 |

| Figure 6-17: Examining the PWM output                                     | 89 |

| Figure 6-18: DC to DC converter                                           | 89 |

| Figure 6-19: Equivalent circuit for switch closed                         | 90 |

| Figure 6-20: Equivalent circuit for switch open                           | 90 |

| Figure 6-21: Examining the PWM output whit open loop controller           | 91 |

| Figure 6-22: Examining the PWM output whit close loop controller          | 91 |

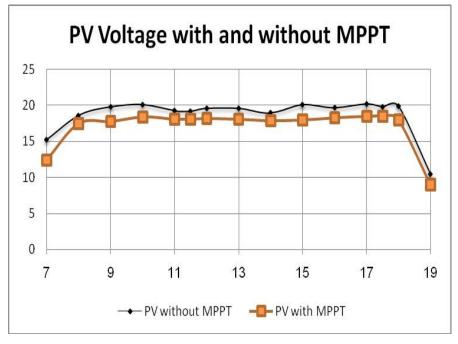

| Figure 6-23: Voltage comparison with and without using MPPT controller    | 93 |

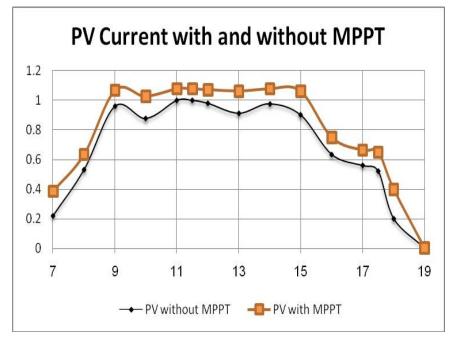

| Figure 6-24: Current comparison with and without using MPPT controller    | 93 |

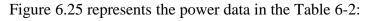

| Figure 6-25: Power comparison with and without using MPPT controller      | 94 |

| Figure 6-26: Power comparison with and without using ST & MPPT controller | 94 |

## List of Abbreviations

| FLC   | Fuzzy Logic Controller                      |

|-------|---------------------------------------------|

| FPGA  | Field Programmable Gate Array               |

| GUI   | Graphical user interface                    |

| PV    | Photo volatic                               |

| MPP   | Maximum Power Point                         |

| VHDL  | Very High Speed Integrated Circuit hardware |

|       | description language                        |

| MPPT  | Maximum Power Point Tracking                |

| PLC   | Programmable Logic Control                  |

| BOS   | Balance of system                           |

| DC    | Direct current                              |

| AC    | Alternating current                         |

| PC    | Personal Computer                           |

| PWM   | Pulse Width Modulation                      |

| GMT   | Generalized modus tollens                   |

| GMP   | Generalized modus pones                     |

| TSK   | Takagi-Sugeno_Kang                          |

| RCOM  | Random choice of maxima                     |

| FOM   | First of maxima                             |

| LOM   | Last of maxima                              |

| MOM   | Middle of maxima                            |

| COG   | Center of gravity                           |

| MOM   | Mean of maxima                              |

| BADD  | Basic defuzzific ation distributions        |

| GLSD  | Generalized level set defuzzific ation      |

| ICOG  | Indexed center of gravity                   |

| SLIDE | Semi-linear defuzzification                 |

| FM    | Fuzzy mean                                  |

|       |                                             |

| WFM  | Weighted fuzzy mean                     |

|------|-----------------------------------------|

| QM   | Quality method                          |

| EQM  | Extended quality method                 |

| COA  | Center of area                          |

| ECOA | Extended center of area                 |

| CDD  | Constraint decision defuzzi_cation      |

| FCD  | Fuzzy clustering defuzzi_cation         |

| PLC  | Programmable logic controller           |

| ASIC | Application-specific integrated circuit |

| IC   | Integrated circuit                      |

| HDL  | Hardware description language           |

| PLD  | Programmable logic devices              |

| PLA  | Programmable logic arrays               |

| CPLD | Complex programmable logic devices      |

| PAL  | Programmable Array Logic                |

| SPLD | Simple programmable logic devices       |

| ADC  | Analog to Digital Converter             |

| DAC  | Digital to Analog Converter             |

| LCD  | Liquid Crystal Display                  |

| PCB  | Printed Circuit Board                   |

| P&O  | Perturbation and Observation            |

| LDR  | Light dependent resistor                |

| UCF  | User constraints file                   |

| DOF  | Degrees of freedom                      |

|      |                                         |

## **CHAPTER 1**

## Introduction

#### **1.1 Introduction**

Renewable energy sources play an important role in electric power generation. There are various renewable sources which used for electric power generation, such as solar energy, wind energy, geothermal etc. Solar Energy is a good choice for electric power generation, since the solar energy is directly converted into electrical energy by solar photovoltaic modules. These modules are made up of silicon cells. When many such cells are connected in series we get a solar PV module. The current rating of the modules increases when the area of the individual cells is increased, and vice versa. When many such PV modules are connected in series and parallel combinations we get a solar PV arrays, that suitable for obtaining higher power output.

The applications for solar energy are increased, and that need to improve the materials and methods used to harness this power source. Main factors that affect the efficiency of the collection process are solar cell efficiency, intensity of source radiation and storage techniques. The efficiency of a solar cell is limited by materials used in solar cell manufacturing. It is particularly difficult to make considerable improvements in the performance of the cell, and hence restricts the efficiency of the overall collection process. Therefore, the increase of the intensity of radiation received from the sun is the most attainable method of improving the performance of solar power. There are three major approaches for maximizing power extraction in solar systems. They are sun tracking, maximum power point (MPP) tracking or both. These methods needs controllers, may be intelligent such as fuzzy logic controller or conventional controller such as PID controller.

The advantage of the fuzzy logic control is that it does not strictly need any mathematical model of the plant. It is based on plant operator experience, and it is very easy to apply. Hence, many complex systems can be controlled without knowing the exact mathematical model of the plant. In addition, fuzzy logic simplifies dealing with nonlinearities in systems. The nice thing about fuzzy logic control is that the linguistic system definition becomes the control algorithm.

The most popular method of implementing fuzzy controller is using a general-purpose microprocessor or microcontroller. Microprocessor based controllers are more economical, but often face difficulties in dealing with control systems that require high processing and input/output handling speeds. Rapid advances in digital technologies have given designers the

option of implementing a controller on a variety of Programmable Logic Device (PLD), Field Programmable Gate Array (FPGA), etc. FPGA is suitable for fast implementation controller and can be programmed to do any type of digital functions. An FPGA has the ability to operate faster than a microprocessor chip. Because of the flexibility of the FPGA, additional functionality and user interface controls can be incorporated into the FPGA minimizing the requirement for additional external components.

FPGAs are programmed using Very High Speed Integrated Circuit hardware description language (VHDL) and a download cable connected to a host computer. Once they are programmed, they can be disconnected from the computer, and it will be running as standalone device. The FPGAs can be programmed while they run, because they can be reprogrammed in the order of microseconds. This short time means that the system will not even sense that the chip was reprogrammed [2]. Applications of FPGAs include industrial motor drivers, real time systems, digital signal processing, aerospace and defense systems, medical imaging, computer vision, speech recognition, cryptography, computer hardware emulation and a growing range of other areas.

The hardware implementation of fuzzy logic controller (FLC) on FPGA is very important because of the increasing number of fuzzy applications requiring highly parallel and high speed fuzzy processing. A significant advantage of this FLC is that it has been coded in VHDL and programmed into a single field programmable gate array (FPGA). Because this reduces the number of electronic components used to implement the controller, it enables redundancy by having multiple copies/images of the code, and yields robustness as a controller that has multiple systems capability[3]. So the FLC may implemented on FPGA and used to moves a motor attached to the solar panel to keep it toward the sun all the day. Then we must chose the kind of the motor as appropriate with the controlled system.

Many applications related to positioning systems are being implemented with stepper motors. It has some applications in Robotics, Computer peripherals, Industrial servo quality drivers and so on. One of the main advantages of stepper motors is the strong relation between electrical pulses and rotation discrete angle steps [1].

3

#### **1.2 Motivation**

Nowadays, fuzzy logic controllers have an efficient performance over the traditional controller researches especially in nonlinear and complex model systems. FPGA is a new key technology used in modern control hardware implementation. Modern manufactures began to apply these technologies in their applications instead of the traditional ones, due to the low cost and widely features available in these controllers. This motivated me to implement FLC on FPGA techniques. In Gaza Strip we have a big problem in electrical power generation, since our sources don't cover all people requirements, electrical power have high cost and many daily interruptions, so we need clean renewable energy sources that do not depend on others such as solar energy since Gaza Strip is 360 km2 and an excellent solar location with 2750 kWh/m2/year irradiation. The electrical problem Gaza has motivated me to investigate Solar Energy as an application to apply my fuzzy controller.

#### **1.3 Objectives**

The main objective is building a FLC using FPGA to maximizing the power output of the solar arrays.

The specific objectives include:

- Designing Fuzzy controllers.

- Realizing controllers on FPGA.

- Building a stepper motor driver.

- Tracking the sun all the day.

#### **1.4 Literature Review**

Daniel A. Pritchard had given the design, development, and evaluation of a microcomputerbased solar tracking system in 1983[4]. Then Manny studies for solar tracking appeared using the microprocessor, Saxena and Dutta in 1990[5], A. Konar and A.K. Mandal in 1991[6], and A. Zeroual in 1997 using electro-optical sensors for sun finding [7]. The microcontroller is used as base for automatic sun tracker to control a dc motor in 1998 by F. Huang [8], and used as base for maximum power point tracking controller by Effichios Koutroulis in 2001[9]. Hasan A. Yousef, had given the PC-based fuzzy logic controller design and Implementation to control a sun tracking system in 1999, the tracking system was driven by two permanent magnet DC motors to provide motion of the PV panels in two axes[10]. Chee-Yee Chong, in 2000 had given the process architectures for track fusion, they presented different approaches for fusing track state estimates, and compared their performance through theoretical analysis and simulations, they used the concept of multiple targets tracking because it had shown that tracking with multiple sensors can provide better performance than using a single sensor[11]. Manny studies for novel maximum power point tracking (MPPT) controller for a photovoltaic (PV) energy conversion system was proposed by Yeong Chau Kuo in 2001[12], K. K. Tse in 2002[13], and Henry Shu-Hung Chung in 2003[14], Kimiyoshi Kohayashi in 2004[15]. Z.G. Piao, proposed a solar tracking system in 2003, using DC motors, special motors like stepper motors, servo motors, real time actuators, to operate moving parts, it was highly expensive [16]. A. A.Khalil, had presented a sun tracking system in 2003, This Tracking system easy to implement and efficient for solar energy collection[17]. Manny methods was proposed to achieve the objective of maximum power point tracking (MPPT), and the active sun tracking scheme without any light sensors, S. Armstrong et al. had proposed a quantitative measure of the effectiveness MPPT efficiency in 2005, a vector methodology was used to track the direction and path of the sun throughout the day[18]. And Rong-Jong Wai. had given grid connected photovoltaic (PV) generation system with an adaptive step-perturbation method and an active sun tracking scheme in 2006[19]. Cemil Sungur had given the electromechanical control system of a photovoltaic (PV) panel tracking the sun using Programmable Logic Controls (PLC) in 2007[20]. Many FPGA-based PV systems fuzzy MPPT control was proposed, A. Messai, A. Mellit describes the hardware implementation of a two-inputs one-output digital Fuzzy Logic Controller (FLC) on a Xilinx FPGA using VHDL language in 2009[21], Cheng, Ze; Yang, Hongzhi; Sun, Ying had proposed a simple, reliable method in 2010[22]. In my study I will construct an efficient solar system with two FLCs have a good response on the same FPGA card.

#### **1.5 Contribution**

In this thesis two fuzzy logic controllers (Sun tracker and MPPT) have been implemented using modern FPGA card (Spartan-3AN, Xilinx Company, 2009), which are used to improve the efficiency of electrical power generated from photovoltaic module. These controllers have been tested using Matlab/Simulink program.

#### **1.6 Outline Of The Thesis**

The thesis is organized into seven chapters. Chapter 2 handles some basic principles of solar energy. Chapter 3 focuses on Fuzzy logic control. Chapter 4 presents full description about FPGA and VHDL software implementation. Chapter 5 presents the design of the sun tracker controller, simulation, results, and the comparison of some results with privies studies. Chapter 6 presents the design of the maximum power point tracker controller, simulation, excremental results. The last chapter concludes the design and the implementation and proposes some future work.

# **CHAPTER 2**

## **Introduction to Solar Energy**

#### 2.1 Background

One of the most important problems facing the world today is the energy problem. This problem is resulted from the increase of demand for electrical energy and raised of fossil fuel prices. Another problem in the world is the global climate change has increased. As these problems alternative technologies for producing electricity have received greater attention. The most important solution was in finding other renewable energy resources [23].

#### 2.1.1 Renewable Energy

Renewable energy is energy which comes from natural resources such as sunlight, wind, rain, tides, and geothermal heat, which are naturally replenished [24]. In its various forms, it derives directly from the sun, or from heat generated deep within the earth [25]. Figure 2.1 show that natural gas and nuclear power are expected to grow slowly over the next 40 years, at which point natural gas will start its decline. It is also hoped that a new clean energy source of fusion energy will be demonstrated at increasing scales from 2030 to 2070 which will then become commercially competitive [26].

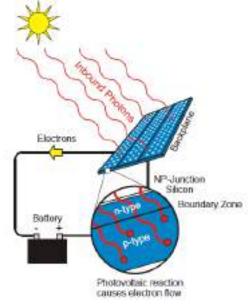

Figure 2-2: Principle of solar cells.

Renewable energy replaces conventional fuels in four distinct areas: power generation, water and space heating, transport fuels, and rural and remote areas energy services [24]. Globally, an estimated 193 million households depends on renewable energy systems [24][27].

The most important of renewable energy is solar energy; however, grid-connected PV increased the fastest of all renewable technologies, with a 60-percent annual average growth rate for the five-year period [24]. Nowadays, solar energy has been widely used in our life, and it's expected to grow up in the next years.

#### 2.1.2 Solar Energy

It's the energy which derived from the sun through the form of solar radiation. Solar powered electrical generation relies on photovoltaic. A partial list of other solar applications includes space and water heating, solar cooking, and high temperature process heat for industrial purposes.

#### 2.2 Photovoltaic Background:

Solar panels are made up of photovoltaic cells; it means the direct conversion of sunlight to electricity by using a semiconductor, usually made of silicon [29]. The word photovoltaic comes from the Greek meaning "light" (photo) and "electrical" (voltaic), The common abbreviation for photovoltaic is PV [30]. Bell Laboratories produced the first solar cell in 1954. The efficiency of this cell was about 5 percent. The first cells were designed for space applications, so the cost was not a major issue. Then solar cell efficiency increased continuously in the following years, and costs have decreased significantly in recent decades. The main material used in the construction of solar cells is still silicon, but other materials have been developed, either for their potential for cost reduction or their potential for high efficiency [30]. Over the last 20 years the world-wide demand for solar electric power systems has grown steadily [28]. The need for low cost electric power in isolated areas is the primary force driving the world-wide photovoltaic (PV) industry today. PV technology is simply the least-cost option for a large number of applications, such as stand-alone power systems for cottages and remote residences, remote telecommunication sites for utilities and the military, water pumping for farmers, and emergency call boxes for highways and college campuses [28].

Solar cells are converting light energy, to another form of energy, electricity. When light energy is reduced or stopped, as when the sun goes down in the evening or when a cloud

passes in front of the sun, then the conversion process stops or slows down. When the sunlight returns, the conversion process immediately resumes, this conversion without any moving parts, noise, pollution, radiation or constant maintenance. These advantages are due to the special properties of semiconductor materials that make this conversion possible. Solar cells do not store electricity; they just convert light to electricity when sunlight is available. To have electric power at night, a solar electric system needs some form of energy storage, usually batteries, to draw upon [31].

#### 2.3 Principle of Solar Cells

Photovoltaic systems employ semiconductor cells (wafers), generally several square centimeters in size [32]. Semiconductors have four electrons in the outer shell, or orbit, on average. These electrons are called valence electrons [30]. When the sunlight hits the photovoltaic cells, part of the energy is absorbed into the semiconductor. When that happens the energy loosens the electrons which allow them to flow freely. The flow of these electrons are a current and when you put metal on the top and bottom of the photovoltaic cells, we can draw that current to use it externally, as shown in Figure 2.2.

Figure 2-2: Principle of solar cells.

Numerous cells are assembled in a module to generate required power [32]. When many such cells are connected in series we get a solar PV module, the current rating of the modules depends on the area of the individual cells. For obtaining higher power output the solar PV modules are connected in series and parallel combinations forming solar PV arrays.

#### 2.4 Types of Solar Panels

There are different types of solar panels which differ in them material, price, and efficiency, since the efficiency is the percentage of solar energy that is captured and converted into electricity. The efficiency values which gives are an average percentage of efficiency, because it's difficult to give an exact number for the different types of solar panels output [29].

• Monocrystalline Solar Panels: have efficiency approximately 18%. They are made from a large crystal of silicon, see Figure 2.3. These types of solar panels are the most efficient as in absorbing sunlight and converting it into electricity; however they are the most expensive. They do somewhat better in lower light conditions than the other types of solar panels.

Figure 2-3 Monocrystalline Solar Panels

• Polycrystalline Solar Panels: have efficiency approximately 15%. Instead of one large crystal, this type of solar panel consists of multiple amounts of smaller silicon crystals, see Figure 2.4.

Figure 2-4 : Polycrystalline Solar Panels.

They are the most common type of solar panels on the market today. They look a lot like shattered glass. They are slightly less efficient than the monocrystalline solar panels and less expensive to produce.

• Amorphous Solar Panels: have efficiency approximately 10%. Consisting of a thin-like film made from molten silicon that is spread directly across large plates of stainless steel or similar material, see Figure 2.5. One advantage of amorphous solar panels over the other two is that they are shadow protected. That means when a part of the solar panel cells are in a shadow the solar panel continues to charge. These types of solar panels have lower efficiency than the other two types of solar panels, and the cheapest to produce. These work great on boats and other types of transportation.

Figure 2-5 : Amorphous Solar Panels.

In this thesis a polycrystalline solar panel is used.

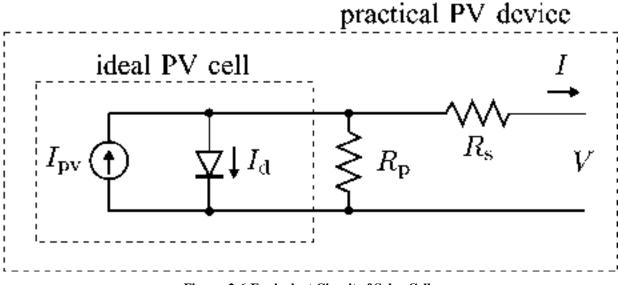

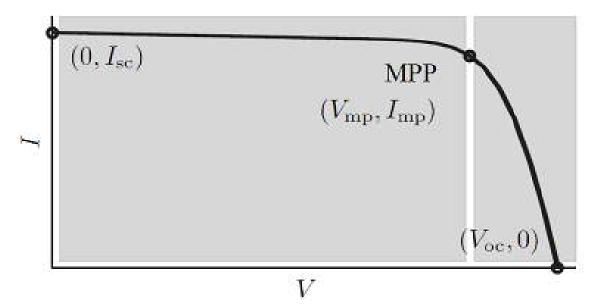

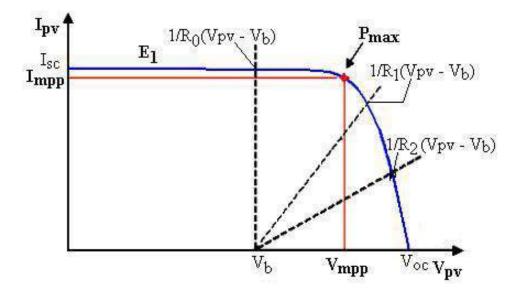

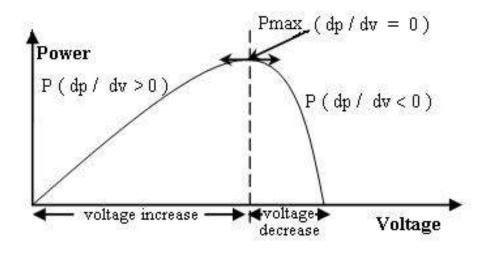

#### 2.5 Equivalent Circuit of a Solar Cell